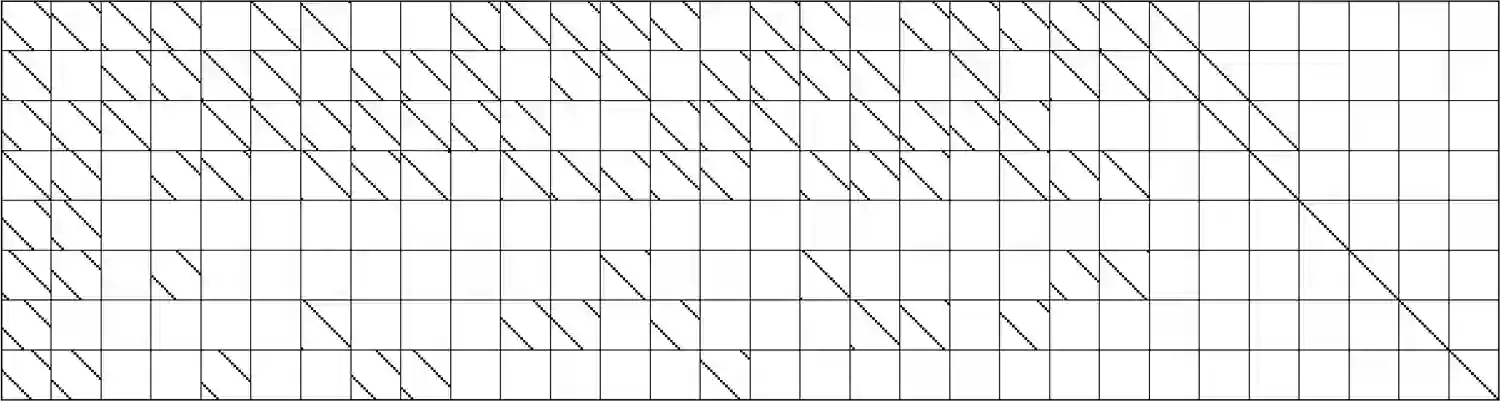

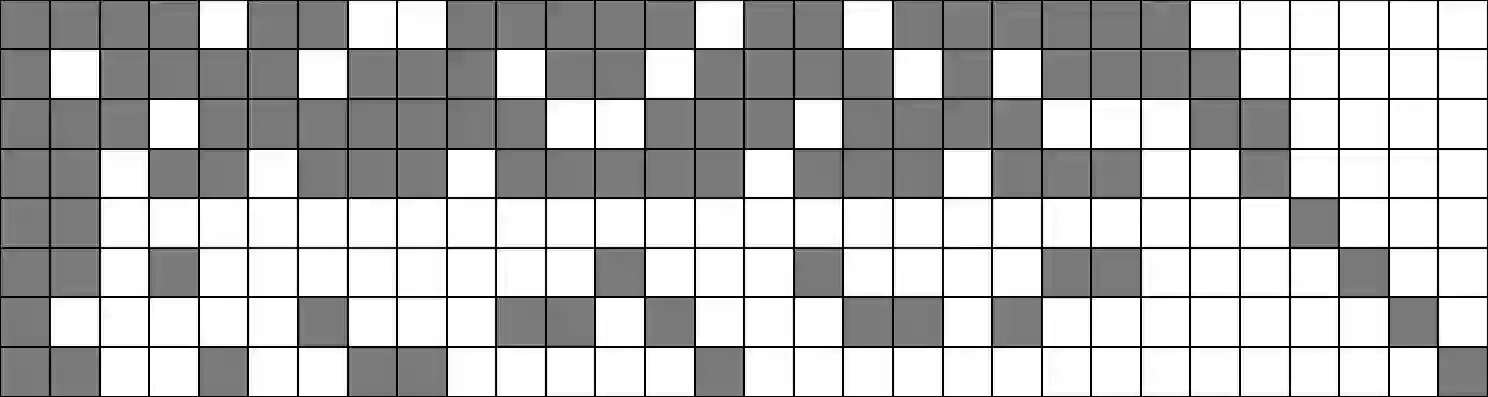

This paper presents novel techniques for improving the error correction performance and reducing the complexity of coarsely quantized 5G-LDPC decoders. The proposed decoder design supports arbitrary message-passing schedules on a base-matrix level by modeling exchanged messages with entry-specific discrete random variables. Variable nodes (VNs) and check nodes (CNs) involve compression operations designed using the information bottleneck method to maximize preserved mutual information between code bits and quantized messages. We introduce alignment regions that assign the messages to groups with aligned reliability levels to decrease the number of individual design parameters. Group compositions with degree-specific separation of messages improve performance by up to 0.4 dB. Further, we generalize our recently proposed CN-aware quantizer design to irregular LDPC codes and layered schedules. The method optimizes the VN quantizer to maximize preserved mutual information at the output of the subsequent CN update, enhancing performance by up to 0.2 dB. A schedule optimization modifies the order of layer updates, reducing the average iteration count by up to 35 %. We integrate all new techniques in a rate-compatible decoder design by extending the alignment regions along a rate-dimension. Our complexity analysis for 2-bit decoding estimates up to 64 % higher throughput versus 4-bit decoding at similar performance.

翻译:本文提出了创新技术,旨在提升粗量化5G-LDPC译码器的纠错性能并降低其复杂度。所提出的译码器设计通过将传递消息建模为条目特定的离散随机变量,支持在基础矩阵级别上实现任意消息传递调度方案。变量节点与校验节点采用基于信息瓶颈方法设计的压缩操作,以最大化保留码比特与量化消息之间的互信息。我们引入了对齐区域,将消息分配至具有对齐可靠性水平的组别,以减少独立设计参数的数量。采用基于度数的消息分离组构成方式,可将性能提升高达0.4 dB。此外,我们将最近提出的校验节点感知量化器设计推广至非规则LDPC码与分层调度方案。该方法通过优化变量节点量化器以最大化后续校验节点更新输出端保留的互信息,从而将性能提升高达0.2 dB。调度优化通过修改层更新顺序,将平均迭代次数降低高达35%。我们通过沿速率维度扩展对齐区域,将所有新技术集成于速率兼容的译码器设计中。针对2比特译码的复杂度分析表明,在相近性能下,其吞吐量较4比特译码最高可提升64%。