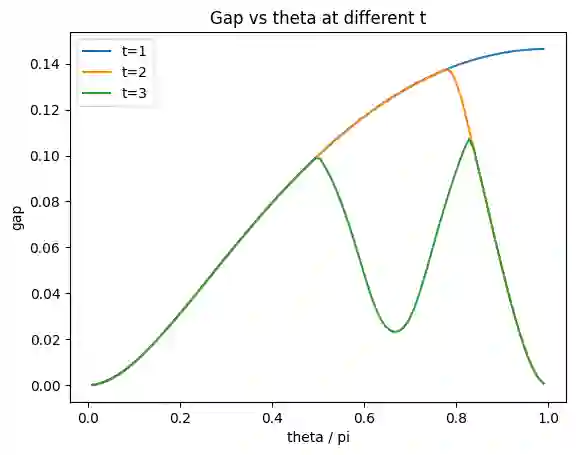

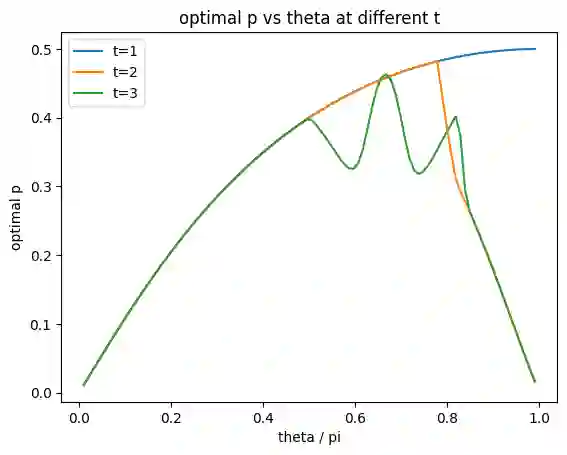

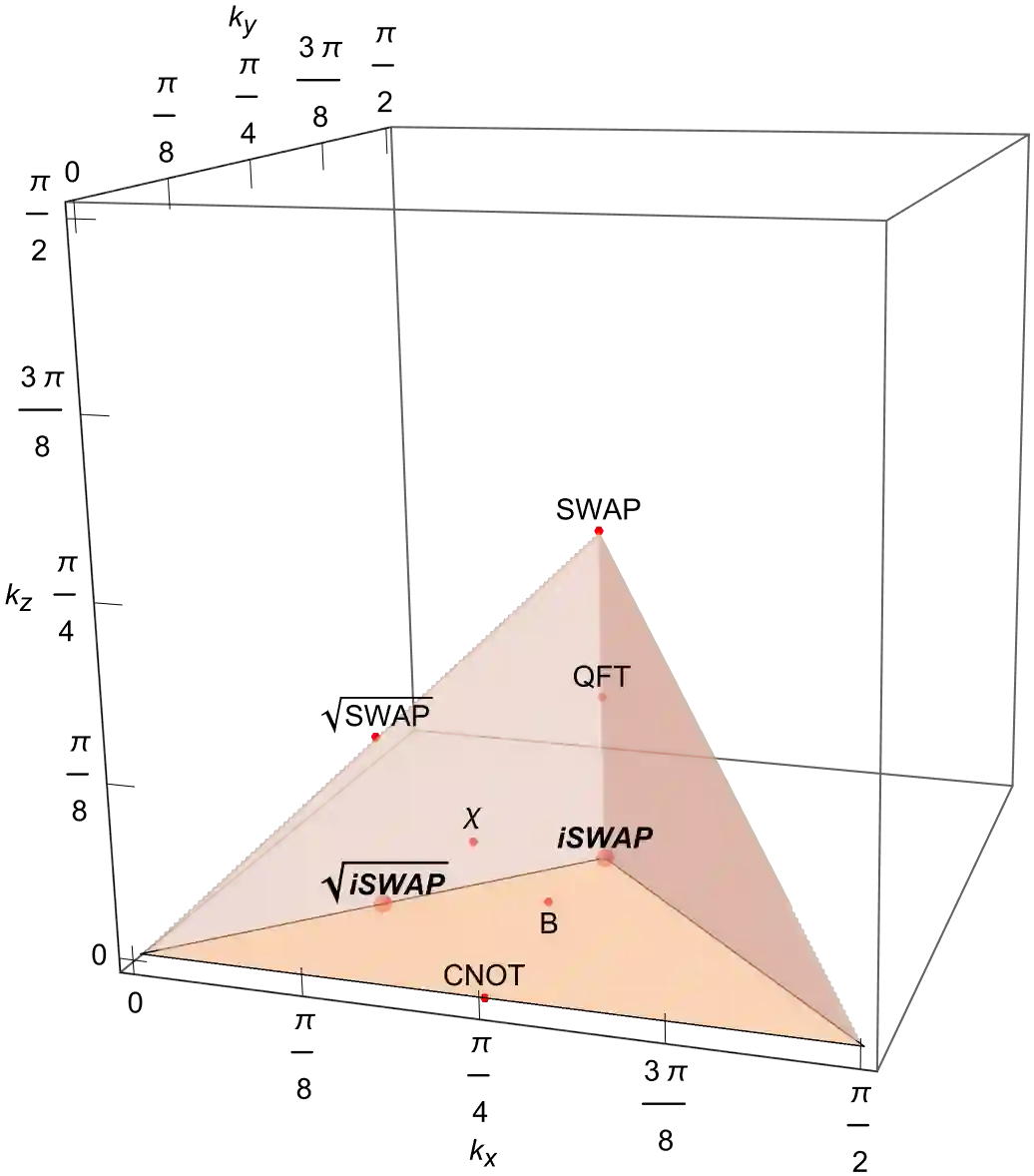

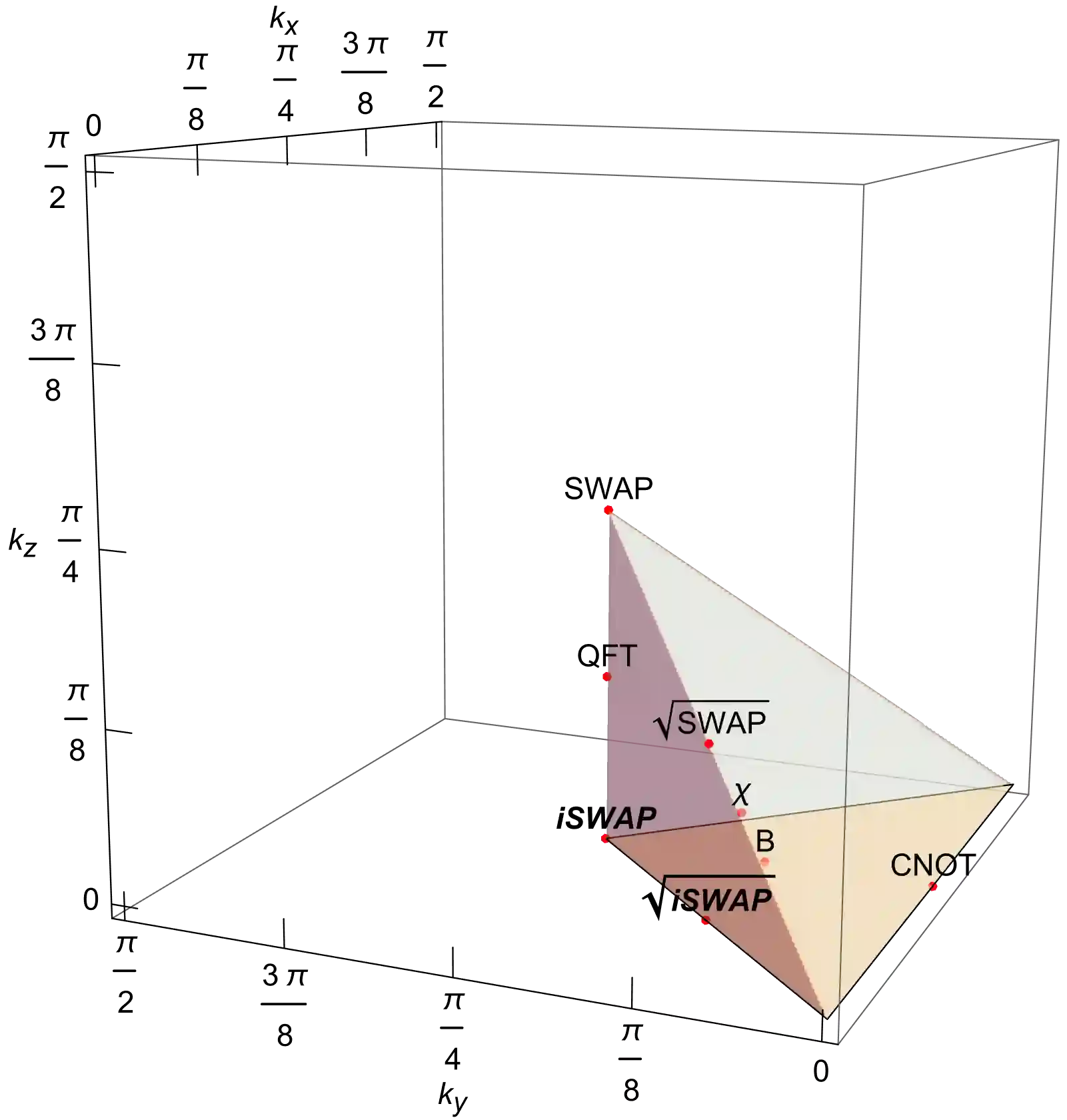

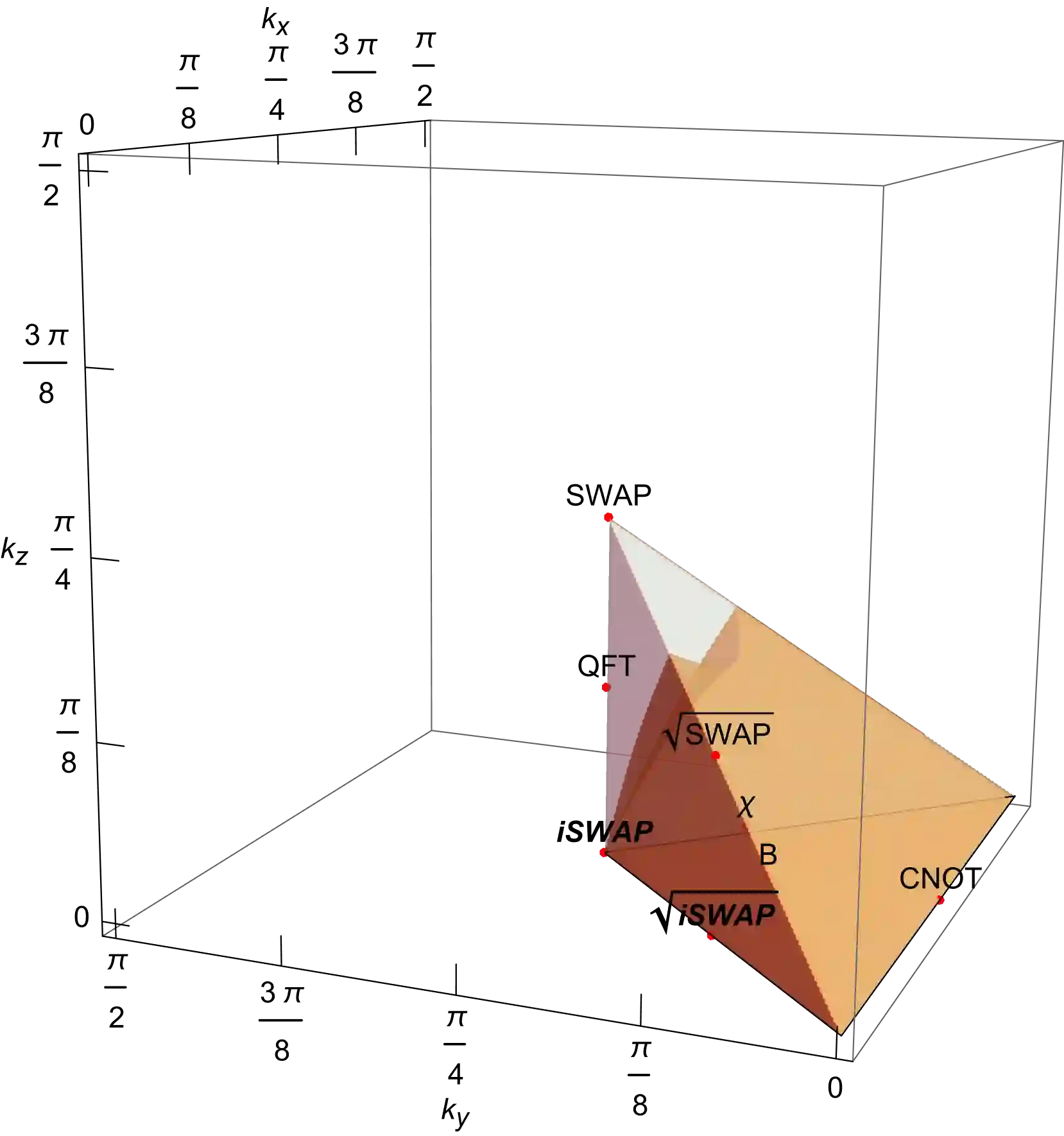

We consider quantum circuit models where the gates are drawn from arbitrary gate ensembles given by probabilistic distributions over certain gate sets and circuit architectures, which we call stochastic quantum circuits. Of main interest in this work is the speed of convergence of stochastic circuits with different gate ensembles and circuit architectures to unitary t-designs. A key motivation for this theory is the varying preference for different gates and circuit architectures in different practical scenarios. In particular, it provides a versatile framework for devising efficient circuits for implementing $t$-designs and relevant applications including random circuit and scrambling experiments, as well as benchmarking the performance of gates and circuit architectures. We examine various important settings in depth. A key aspect of our study is an "ironed gadget" model, which allows us to systematically evaluate and compare the convergence efficiency of entangling gates and circuit architectures. Particularly notable results include i) gadgets of two-qubit gates with KAK coefficients $\left(\frac{\pi}{4}-\frac{1}{8}\arccos(\frac{1}{5}),\frac{\pi}{8},\frac{1}{8}\arccos(\frac{1}{5})\right)$ (which we call $\chi$ gates) directly form exact 2- and 3-designs; ii) the iSWAP gate family achieves the best efficiency for convergence to 2-designs under mild conjectures with numerical evidence, even outperforming the Haar-random gate, for generic many-body circuits; iii) iSWAP + complete graph achieve the best efficiency for convergence to 2-designs among all graph circuits. A variety of numerical results are provided to complement our analysis. We also derive robustness guarantees for our analysis against gate perturbations. Additionally, we provide cursory analysis on gates with higher locality and found that the Margolus gate outperforms various other well-known gates.

翻译:本文研究量子电路模型,其中量子门是从由特定门集和电路架构上的概率分布给出的任意门系综中抽取的,我们称之为随机量子电路。本工作的主要关注点在于具有不同门系综和电路架构的随机电路收敛至酉t-设计的速率。该理论的一个关键动机在于不同实际场景中对不同量子门和电路架构的偏好差异。特别地,它提供了一个通用框架,用于设计实现t-设计的高效电路及相关应用,包括随机电路与置乱实验,以及对量子门和电路架构的性能基准测试。我们深入研究了多种重要设定。本研究的一个关键方面是“熨平模块”模型,该模型使我们能够系统评估和比较纠缠门与电路架构的收敛效率。特别值得注意的结果包括:i)具有KAK系数$\left(\frac{\pi}{4}-\frac{1}{8}\arccos(\frac{1}{5}),\frac{\pi}{8},\frac{1}{8}\arccos(\frac{1}{5})\right)$的双量子位门模块(我们称之为$\chi$门)可直接构成精确的2-设计和3-设计;ii)在具有数值证据的温和猜想下,iSWAP门族在通用多体电路中实现2-设计收敛的效率最优,甚至超越Haar随机门;iii)在所有图电路中,iSWAP+完全图架构实现2-设计收敛的效率最优。我们提供了多种数值结果以补充理论分析。同时推导了分析结果对门扰动的鲁棒性保证。此外,我们对更高局域性的门进行了初步分析,发现Margolus门优于多种其他知名门。